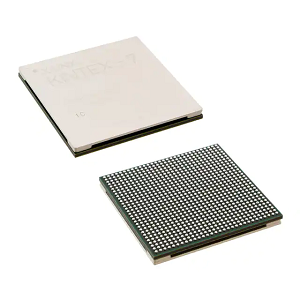

XC7K420T-2FFG901I – integrované obvody, vestavěné, programovatelné pole hradel

Vlastnosti produktu

| TYP | ILUSTROVAT |

| kategorie | Integrované obvody (IC)Vložené Field Programmable Gate Arrays (FPGA) |

| výrobce | AMD |

| série | Kintex®-7 |

| zabalit | zásobník |

| Stav produktu | Aktivní |

| DigiKey je programovatelný | Neověřeno |

| Číslo LAB/CLB | 32575 |

| Počet logických prvků/jednotek | 416960 |

| Celkový počet bitů RAM | 30781440 |

| Počet I/O | 380 |

| Napětí - Napájení | 0,97V ~ 1,03V |

| Typ instalace | Typ povrchového lepidla |

| Provozní teplota | -40 °C ~ 100 °C (TJ) |

| Balíček/Bydlení | 900-BBGA, FCBGA |

| Zapouzdření komponent dodavatele | 901-FCBGA (31x31) |

| Hlavní číslo produktu | XC7K420 |

| TYP | ILUSTROVAT |

| kategorie | Integrované obvody (IC)Vložené |

| výrobce | AMD |

| série | Kintex®-7 |

| zabalit | zásobník |

| Stav produktu | Aktivní |

| DigiKey je programovatelný | Neověřeno |

| Číslo LAB/CLB | 32575 |

| Počet logických prvků/jednotek | 416960 |

| Celkový počet bitů RAM | 30781440 |

| Počet I/O | 380 |

| Napětí - Napájení | 0,97V ~ 1,03V |

| Typ instalace | Typ povrchového lepidla |

| Provozní teplota | -40 °C ~ 100 °C (TJ) |

| Balíček/Bydlení | 900-BBGA, FCBGA |

| Zapouzdření komponent dodavatele | 901-FCBGA (31x31) |

| Hlavní číslo produktu | XC7K420 |

FPGA

Výhody

Výhody FPGA jsou následující:

(1) FPGA se skládají z hardwarových zdrojů, jako jsou logické buňky, RAM, násobiče atd. Racionálním uspořádáním těchto hardwarových zdrojů lze implementovat hardwarové obvody, jako jsou násobiče, registry, generátory adres atd.

(2) FPGA lze navrhovat pomocí blokových diagramů nebo Verilog HDL, od jednoduchých hradlových obvodů po obvody FIR nebo FFT.

(3) FPGA lze nekonečně přeprogramovat, načíst nové konstrukční řešení během několika stovek milisekund, a to pomocí rekonfigurace pro snížení hardwarové režie.

(4) Pracovní frekvence FPGA je dána FPGA čipem i konstrukcí a může být upravena nebo nahrazena rychlejším čipem pro splnění určitých náročných požadavků (i když samozřejmě pracovní frekvence není neomezená a může zvýšit, ale řídí se aktuálními procesy IC a dalšími faktory).

Nevýhody

Nevýhody FPGA jsou následující:

(1) FPGA spoléhají na hardwarovou implementaci pro všechny funkce a nemohou implementovat operace, jako je větvení podmíněných skoků.

(2) FPGA mohou implementovat pouze operace s pevným bodem.

Stručně řečeno: FPGA se při implementaci všech funkcí spoléhají na hardware a lze je srovnávat s vyhrazenými čipy, pokud jde o rychlost, ale existuje velká mezera ve flexibilitě návrhu ve srovnání s procesory pro obecné použití.

Návrhové jazyky a platformy

Programovatelná logická zařízení jsou hardwarové nosiče, které konkretizují zavedené funkce a technické specifikace elektronických aplikací prostřednictvím technologie EDA.FPGA jako jedno z mainstreamových zařízení, které implementují tuto cestu, jsou přímo uživatelsky orientované, extrémně flexibilní a všestranné, snadno použitelné a rychle testovatelné a hardwarové.

Hardware Description Language (HDL) je jazyk používaný k navrhování digitálních logických systémů a popisu digitálních obvodů, hlavními běžně používanými jsou VHDL, Verilog HDL, System Verilog a System C.

Jazyk VHDL (Very High Speed Integrated Circuit Hardware Description Language) jako všestranný jazyk pro popis hardwaru má vlastnosti nezávislé na konkrétním hardwarovém obvodu a nezávislé na platformě návrhu, s výhodami schopnosti širokého popisu, nikoli závislé na konkrétních zařízeních a schopnost popsat návrh složité řídicí logiky v přísném a stručném kódu atd. Je podporován mnoha společnostmi EDA a je široce používán v oblasti elektronického designu.široce používaný.

VHDL je vysokoúrovňový jazyk pro návrh obvodů a ve srovnání s jinými jazyky pro popis hardwaru má vlastnosti jednoduchého jazyka, flexibility a nezávislosti na návrhu zařízení, což z něj činí běžný jazyk popisu hardwaru pro technologii EDA a činí technologii EDA lepší. přístupné designérům.

Verilog HDL je široce používaný jazyk pro popis hardwaru, který lze použít ve více fázích procesu návrhu hardwaru, včetně modelování, syntézy a simulace.

Výhody Verilog HDL: podobně jako C, snadno se učí a je flexibilní.Citlivý na velká písmena.Výhody při psaní podnětů a modelování.Nevýhody: mnoho chyb nelze zjistit v době kompilace.

Výhody VHDL: Přísná syntaxe, jasná hierarchie.Nevýhody: dlouhá doba seznamování, nedostatečně flexibilní.

Software Quartus_II je kompletní multiplatformní návrhové prostředí vyvinuté společností Altera, které dokáže splnit konstrukční potřeby různých FPGA a CPLD a je komplexním prostředím pro návrh programovatelných systémů na čipu.

Vivado Design Suite, integrované návrhové prostředí vydané dodavatelem FPGA Xilinx v roce 2012. Zahrnuje vysoce integrované návrhové prostředí a novou generaci nástrojů od úrovně systému až po IC, vše postavené na sdíleném škálovatelném datovém modelu a společném ladicím prostředí.Xilinx Vivado Design Suite poskytuje jádra FIFO IP, která lze snadno aplikovat na návrhy.